Design Tools Adiabatic Quantum Flux Parametron

Design methods and tools for superconducting electronics

Siang-Yun Lee, Dewmini Marakkalage , Siang-Yun Lee, Alessandro Tempia Calvino, Eleonora Testa and Giovanni De Micheli

The growing interest in superconducting electronics (SCE) is related to the search for a scalable computing technology that can match and extend the current performances of CMOS at lower energy cost. The SCE technology will be very relevant to the design of fast computing systems in the twenties, to address challenging complex computational problems as, for example, related to artificial intelligence, security, weather prediction and environmental modeling as well as bio-med-discovery and drug design. Whereas prototype circuits of medium scale have been successfully designed and tested, the realization of complex and powerful computing systems is hindered by the lack of design tools. Indeed, the features of various incarnations of SCE, such as rapid single flux quantum (RSFQ) and adiabatic quantum flux parametron (AQFP) circuits - that support deeply pipelined and/or wave pipelined circuits - render design more complex.

There are few commercial design tools for logic and physical design of SCE and research tools can cope only with limited-scale design. It is the purpose of this research to provide a framework for the logic design of SCE circuits with various technological flavors. Thus this project addresses:

- logic models that capture common features as well as competitive advantages of different SCE realizations;

- algorithms that manipulate models in the search for optimal implementation in terms of performance (i.e., latency) and area;

- synthesis and optimization software tools that enable designers to map functional specifications of SCE systems in register-transfer languages (RTL) to optimized netlists of logic gates;

- algorithms and tools for verifying implementation correctness.

Synthesis and Optimization for Emerging Technologies in Superconducting Electronics

The growing demand for computationally-heavy applications nowadays draws increasing attention to superconducting electronics (SCE) because of its capability of high-speed computation and low energy consumption. In parallel to the rapid development of SCE technologies such as the rapid single-flux quantum (RSFQ) and the adiabatic quantum-flux parametron (AQFP), there is a need to adapt the existing electronic design automation (EDA) algorithms to address the design constraints arising from these emerging technologies.In particular, two special constraints are imposed by both RSFQ and AQFP circuits:

- Path balancing: Logic gates in both AQFP and RSFQ are clocked, and the input signals of a logic gate must arrive at the same time. In other words, all data paths must have the same length. Whereas shortening longer paths is not always possible, buffers can be inserted to delay shorter paths.

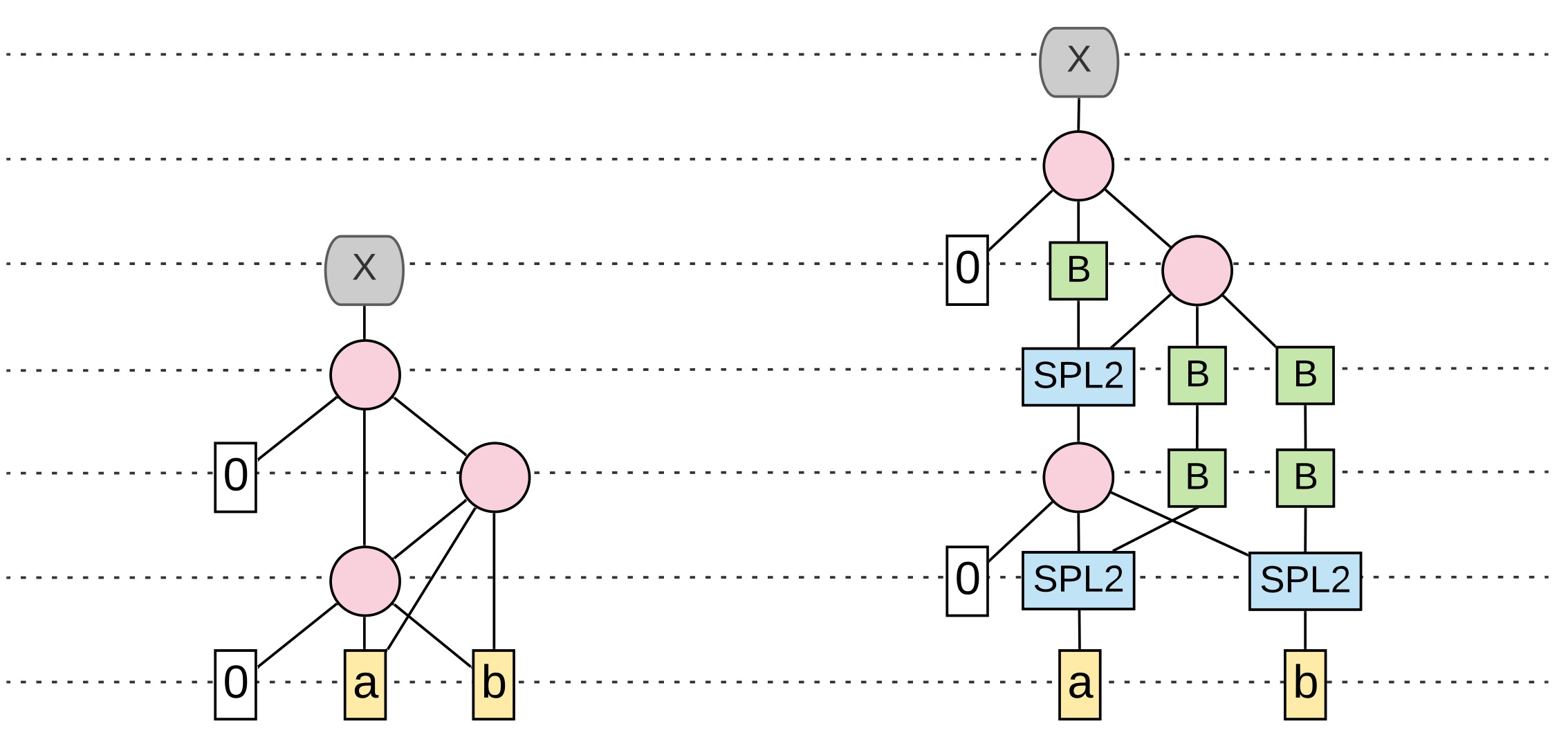

- Fanout branching: As the output current of an AQFP gate, or the output pulse of an RSFQ gate, is limited, it has to be amplified by a splitter before branching into multiple fanouts. In AQFP, splitters are clocked (i.e., participate in path balancing); in RSFQ, splitters are not clocked.

Logic synthesis and optimization for Adiabatic Quantum-Flux-Parametron (AQFP) Circuits

Adiabatic Quantum-Flux-Parametron (AQFP) is a family of superconducting electronic (SCE) circuits exhibiting high energy efficiency. In AQFP technology, logic gates require splitters to drive multiple fanouts and both the logic gates and the splitters are clocked, requiring path balancing using buffers to ensure all fanins of a gate arrive simultaneously.

The path balancing and splitter requirements of the AQFP technology pose additional challenges in logic synthesis because buffers and splitters also significantly affect the area and delay of a circuit. Hence, CMOS-focused synthesis tools are ineffective for AQFP optimizations, and consequently, there have been several attempts to optimize the splitter insertion and path balancing of AQFP circuits. However, we have identified several weaknesses of such existing approaches, namely i) lack of consideration for interdependent logic paths, ii) the bias towards using balanced splitter trees, and iii) the lack of support for more complex logic gates such as majority-5.

We have recently proposed a method to mitigate the aforementioned issues using exact synthesis on small blocks of logic in a given logic network. Indeed such methods are impractical on logic blocks with 5 inputs or more. Our synthesis algorithm performs simultaneous optimizations of logic and path balancing resources that capture more optimization opportunities as compared to prior work in the field and achieves much improved circuits in terms of both area and delay. It uses a two-step approach which first generates a database of optimum AQFP structures for 4-input logic function, and then rewrites 4-input logic blocks in a larger network using the generated database. However, the way the current algorithm chooses the logic blocks that are to be rewritten is independent from the generated database. We thus continue to work on improving the rewriting step to adaptively choose logic blocks to be rewritten, and we expect such an algorithm to produce improved AQFP circuits. Additionally, we also aim to improve the database generation process in order to support frequently occurring 5- and 6-input functions.

Splitting and balancing in AQFP. Left: Original logic network. Right: Feasible realization where two-output splitters are inserted and buffers to make the circuit balanced.

Main recent publications

- Eleonora Testa, Siang-Yun Lee, Heinz Riener, and Giovanni De Micheli. "Algebraic and Boolean Optimization Methods for AQFP Superconducting Circuits," 2021 Asia and South Pacific Design Automation Conference (ASP-DAC).

- Siang-Yun Lee, Heinz Riener, and Giovanni De Micheli. "Irredundant Buffer and Splitter Insertion and Scheduling-Based Optimization for AQFP Circuits," 2021 International Workshop on Logic and Synthesis (IWLS).

- D. S. Marakkalage, H. Riener, and G. De Micheli, "Optimizing Adiabatic Quantum-Flux-Parametroc Circuits using Exact Methods," 2021 International Workshop on Logic and Synthesis (IWLS), YouTube: https://youtu.be/NptadKYzhBU .

Design Tools Adiabatic Quantum Flux Parametron

Source: https://si2.epfl.ch/~demichel/research/supercool.html

Posted by: mallarduntes1948.blogspot.com

0 Response to "Design Tools Adiabatic Quantum Flux Parametron"

Post a Comment